“The BB5 family supports voltage options from 1.8 to 5.5V, allowing them to last for years in the field on a coin-cell battery,” according to the company. “They also come in a variety of packing sizes, from 2 x 2mm for BB50, while BB51 and BB52 are 3 x 3mm offering additional GPIOs and increased analog functionality.”

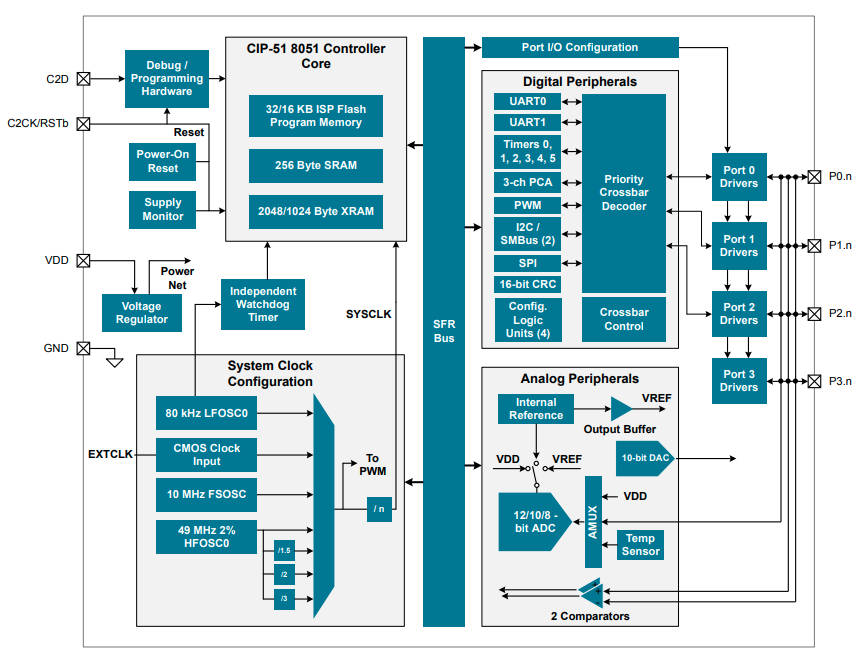

The fundamental difference between these three sub-families is in the analogue perpherals: BB2 is the superset (see diagram), with a 12bit ADC, two comparators and a 10bit DAC. BB51 looses the DAC, and BB50 further looses the comparators. All three get a programmable internal reference (1.2 – 2.4V), a reference input, and ‘fast-settling’ (5µs max) adjustable (1.2 – 1.8V) internal voltage reference.

CIP-51 is a pipelined core that can hit 50Mips peak throughput with its 50MHz clock. “Any standard

803x/805x assemblers and compilers can be used to develop software,” said the company. “CIP-51 implements standard 8051 organisation and peripherals, as well as additional custom peripherals

and functions.”

Extensions include power management modes – there is a 10µA snooze mode with a 30µs wake, debug logic, interrupt handler extensions and security for program and data memory.

Up to 29 I/O pins are implemented (depending on the package) and peripherals include a temperature sensor, three-channel ‘programmable counter array’ with PWM capability, a three-channel PWM engine with dead-time insertion, 4x 16bit timers, 2x 8bit timers, 2x UART, 2x SMBus/I2C, SPI (with 4byte FIFO), 4x configurable logic units and crossbar pin mapping.