Marvell’s 3nm silicon building blocks include 112G XSR SerDes Long Reach SerDes, PCIe Gen 6 / CXL 3.0 SerDes, and a 240 Tbps parallel die-to-die interconnect.

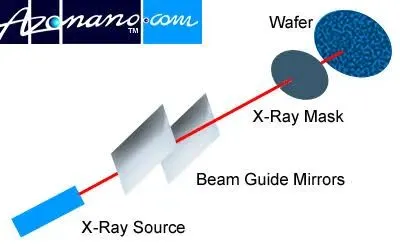

These technologies also support all semiconductor packaging options from standard and low-cost RDL (Redistribution Layers) to silicon-based high-density interconnect.

The new parallel die-to-die interconnect enables aggregate data transfers up to 240 Tbps.

The SerDes and interconnect technologies are incorporated into Marvell’s flagship silicon solutions including Teralynx switches, PAM4 and coherent DSPs, Alaska Ethernet physical layer (PHY) devices, OCTEON processors, Bravera storage controllers, Brightlanecautomotive Ethernet chipsets, and custom ASICs.

Moving to a 3nm process enables engineers to lower the cost and power consumption of chips and computing systems while maintaining signal integrity and performance.

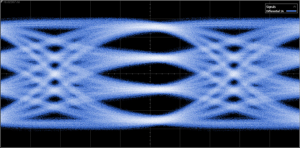

|

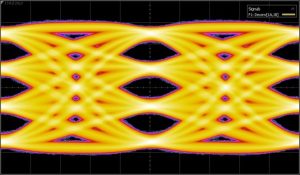

PCIe Gen 6 SerDes (@ 64Gb/s) |

112G XSR SerD (@ 113 Gb/s) |

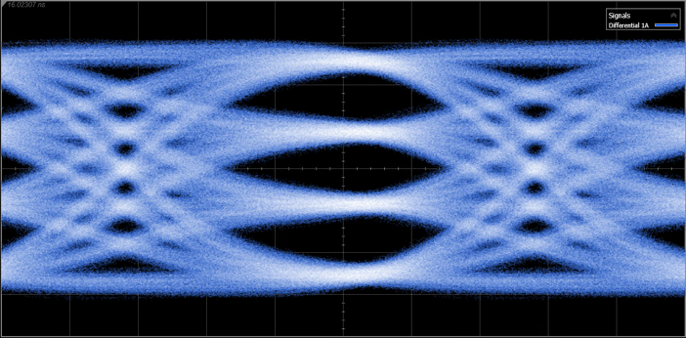

Caption: The blue eye diagram represents high-performance signals transmitted by Marvell’s 3nm SerDes optimized for PCIe Gen 6 / CXL 3.0 while the orange represents the signals from its 3nm low latency SerDes optimized for 112G XSR. Both are industry firsts. The vertical height, size, and relative symmetry of the eyes indicate the mitigation of noise and bit errors