The flip-side are the disadvantages, warranting a mushrooming component count to temper them.

Enter the University of California, San Diego, which, together with France’s CEA-Léti semiconductor lab, decided to build a custom IC to swallow any number of transistors required to beat the problems, and their results were revealed at the International Solid-State Conference in San Francisco this week.

The switched-capacitor bookends allow the converter to have a high input to output ratio, varying around 10:1 in this case, without falling far from peak efficiency.

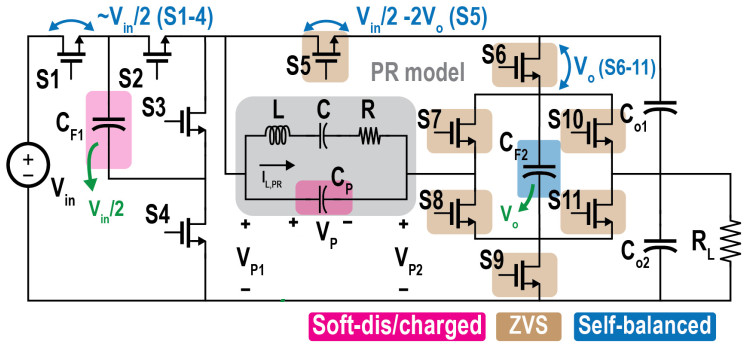

The end capacitive converters share transistors with the central piezoelectric converter, and all switches are controlled using a seven-phase cycle, with many of them switching with zero volts across them to increase efficiency – the switches are all n-mos transistors, integrated into the IC.

The result converts 16 – 20Vin to 1.1 – 2.2Vout at 113 – 129kHz.

Peak efficiency (88.7%), is when converting 20V to 2.2V at 100mA (220mW).

Along with the resonator, the power components are: 6mm2 of 180nm BCD silicon real estate, 4×10μF 0603 flying and output capacitors, and 9x 150nF 0402 bootstrap capacitors – adding up to 0.6cm2. On top of this is a microcontroller board providing the control signals.

As relatively high voltages need to be switched, in reality some of the switches are series stacks of transistors, with power for their gate drives generated by a stacked bootstrap arrangement – hence the need for so many bootstrap capacitors.

It is traditional at ISSCC to present a table comparing the subject of a paper to the previous state-of-the art, but so rare are piezoelectric converters – the researchers could only find a handful – that they built their own competitors for comparison.

Using the same resonator, plus discrete transistors (GaN for maximum efficiency), they built just the central piezoelectric resonant converter (4x GaN transistors), and then added a front-end switched capacitor converter to that (4x+3x transistors).

These occupied 8.16 and 14.28cm2 respectively (plus the external controller), and operated at 71.7 and 78.7% efficiency.

ISSCC 2024 paper 8.6: ‘An integrated dual-side series/parallel piezoelectric resonator-based 20-to-2.2V dc-dc converter achieving a 310% loss reduction’

Image credit: ISSCC 2024 paper 8.6 University of California, San Diego, CEA-Léti

ISSCC, the annual International Solid-State Circuits Conference in San Francisco, is the world’s shop window for circuit advances aimed at ICs – Attendees are exposed, literally, to the state-of-the-art.