Starting with that headphone amplifier: Class-H is a way to decrease the dissipation of an analogue output stage by getting its power rails to track the envelope of the audio signal, just enough above the audio signal level for the output devices to operate cleanly.

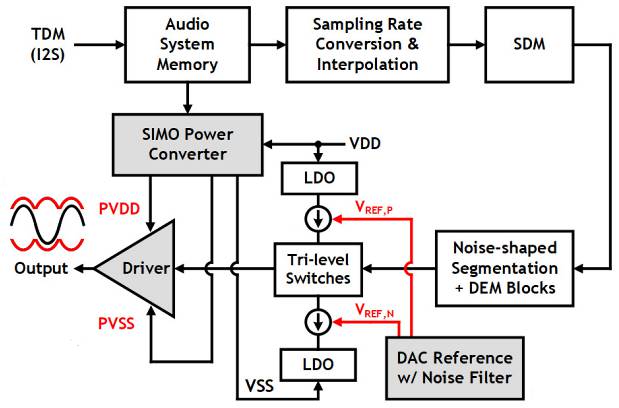

Created by a team from MediaTek, their headphone amplifier uses a SIMO (single-inductor multiple-output) dc-dc converter to generate two tracking power rails, one positive and one negative, plus a fixed supply for the rest of the circuitry. The tracking rails are very agile, with a bandwidth of 3kHz.

Tracking is controlled by getting an early look at the coming audio stream by intelligently dipping into memory storing the forthcoming audio.

The controller balances its timings to slew the variable rails from ±300mV to ±1.8V (silence to 62mW into the 16Ω audio load), with a special scheme to prevent over-charging the converter’s output capacitors at audio outputs below 10mW – as the output transistors would have to waste any excess.

This power-aware scheme is said to increase signal path efficiency from 33% to 45% at 10mW.

Overall performance is -108dBc THD+N (-112dB THD only) and 126dB (A-weighted) dynamic range. Consumption is 28.7mW from the 1.8V input rail for 10mW of audio output.

Turning to power amplifiers, Delft University of Technology and Goodix Technology teamed up to present papers on two Class-D audio amplifiers, both running from 14.4V (’12V’ vehicle voltage) and driving 8Ω loud speakers.

The first was a filter-less deign – without an LC output filter – delivering 12.7W into 8Ω, with distortion remaining below -90dB at 8W.

Headline figures are: 90% efficiency, a dynamic range of 121.7dB and -109.0dB peak THD+N – from a 7.9mm2 0.18μm BCD IC.

Despite having a digital input signal and a switching output, the signal is reduced to an analogue form by a current output DAC part-way through the signal chain, where feedback from the output terminals is circulated, before it is PWM-modulated for the output stage.

The second amplifier, a 14W design, had an LC filter around which current feedback was wrapped to remove nonlinearities, including those introduced by the filter.

Creating a stable loop in these circumstances is already difficult, but the development team also added requirements to tolerate 30% variation in the L and C values, and to use a 530kHz cut-off to keep the filter components physically small (L=2 x 1.25 x 1mm).

THD+noise measured at -105dB, and dynamic range at 109dB (A). Power efficiency is over 90%.

At the other end of a digital audio stream, a coupe of audio ADCs were also discussed.

For far-field voice input with low-cost microphones, a design from Texas Instrument’s Bangalore office prioritises dynamic range over signal-to-noise ratio.

It achieves 118.5dB A-weighted range (116.3dB un-weighted) abd works over 20Hz to 20kHz, while consuming 3.3mW. Maximum SNDR (signal-to-noise and distortion ratio) is 103.9dB with a -4.5dBfs input.

Architecturally it is a continuous-time ΔΣ modulator, chosen for its inherent anti-aliasing

and resistive input.

Fabricated in 130nm mixed-signal cmos, the circuit occupies 0.48mm2, and its analogue consumes 505μA from 3.3V plus 652μA from 1.8V, while the digital parts need 263μA from 1.8V supply.

Lastly National Cheng Kung University presented a 100kHz bandwidth 4th-order noise-shaping SAR (successive approximation) ADC for IoT applications, which achieves 94.3dB SNDR (94.4dB signal-to-noise ratio) on a 28nm process while consuming 107μW from a 1V rail. SFDR (spurious-free dynamic range is 106.8dB over 100kHz.

First and third-order integration are implemented by dynamic-amplifier-assisted integration, while second and fourth-order integration are implemented by passive charge sharing.

“By using the cascaded integrators with dynamic-amplifier-assisted integration to realize

4th-order NS, this work avoids mild noise transfer function, possesses PVT [process, voltage, temperature] robustness even in the presence of significant amplifier gain variations, and requires fewer amplifiers.” according to the university in ISSCC presentation 9.7.

ISSCC 21.4 A -108dBc THD+N, 2.3mW Class-H headphone amplifier with power-aware SIMO supply modulator

ISSCC 21.1 A 121.7dB DR and -109.0dB THD+N filterless digital-input Class-D amplifier with an HV multibit IDAC using tri-level output and employing a transition-rate-balanced bidirectional RTDEM scheme

ISSCC 21.3 A -106.3dB THD+N feedback-after-LC Class-D audio amplifier employing current feedback to enable 530kHz LC-filter cut-off frequency

ISSCC 21.2 A 0.81mA, -105.2dB THD+N Class-D audio amplifier with capacitive feedforward and PWM-aliasing reduction for wide-band-effective linearity lmprovement

ISSCC 9.5 A 118.5dBA DR 3.3mW audio ADC with a Class-B resistor DAC, non-overlap DEM and continuous-time quantizer

ISSCC 9.7 A 94.3dB SNDR 184dB FoMs 4th-order noise-shaping SAR ADC with dynamic-amplifier-assisted cascaded integrator

ISSCC, the annual International Solid-State Circuits Conference in San Francisco, is the world’s shop window for circuit advances aimed at ICs – Attendees are exposed, literally, to the state-of-the-art.