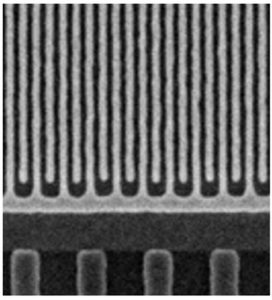

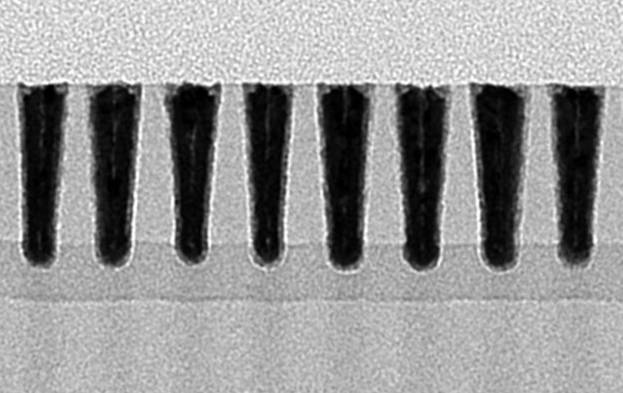

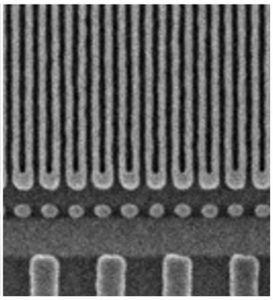

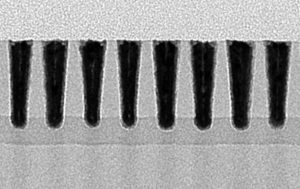

Top-down SEM pictures of 20nm pitch meanders after pattern transfer into TiN hard mask

Metal oxide negative tone resist was used, and yield was over 90%.

“This is the first ever electrical yield demonstration of 20nm pitch metal lines obtained with single high NA EUV patterning,” said Imec R&D v-p Steven Scheer. “These results represent an initial validation of the capabilities of high NA EUV lithography and its ecosystem, including resists, under-layers, photomasks, metrology, imaging and optical proximity correction, well as integrated patterning and etch.”

This performance metric was obtained on two different test structures: serpentine (aka meander, above right) and fork-fork (below left).

“When combined with e-beam inspection, conductivity measurements of metallised serpentine and fork-fork structures give information on the stochastic defects – breaks and bridges, respectively,” said Imec director of patterning Philippe Leray.

The lab teamed up with Dutch semiconductor equipment maker ASML on the ecosystem, aimed at sub-2nm ICs, and brought in suppliers of materials, resists, masks and metrology, and chip manufacturers.

Results are being presented this week at SPIE Advanced Lithography + Patterning in San Francisco in two papers :

‘Probing defects in metal oxide resists with an electrical yield vehicle’

‘Advanced PnR logic patterning enabled by high-NA EUV lithography’.