Called the EPYC 8004 series, they are multi-chiplet ICs with up to 64 of the company’s ‘Zen 4c’ cores – a slower version of the Zen 4 – fitting the company’s new smaller (SP6) socket, and are aimed at space and infrastructure constrained environments.

Across the series are between 8 and 64 cores and 16 to 128 threads, with a choice of L3 caches size and operating temperatures (see table).

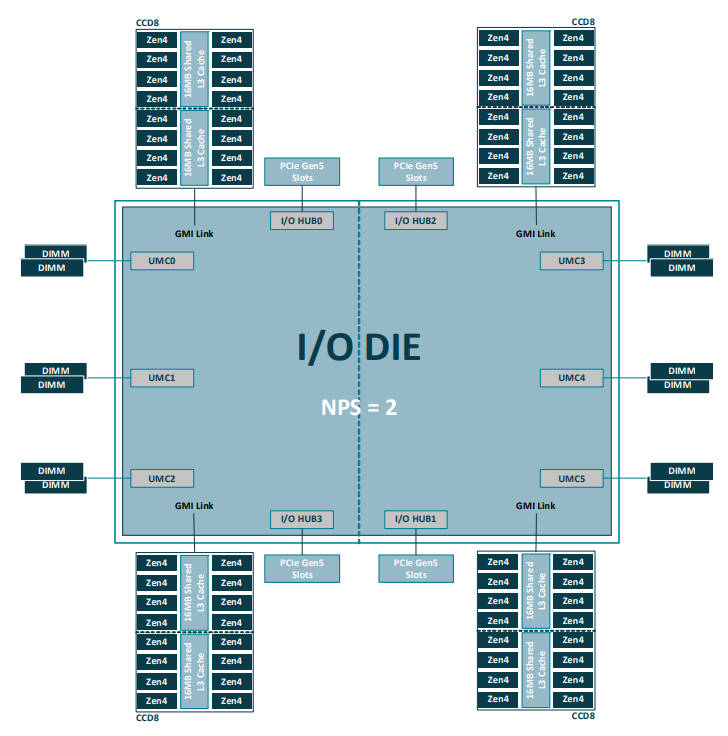

They have up to 96 high-speed I-O lanes (3x G-Link and 3x P-link =6 x 16). “The three G-links provide 48 lanes of PCI Gen5 support, the three P-links can be used for 48 lanes of CXL [Compute eXpress Links] 1.1+ support or 48 lanes of PCI Gen5 support. Alternatively, you can use 32 of the lanes for SATA,” said AMD.

Up to six 4,800MHz DDR5 channels are included to access up to 1.152 or 3Tbyte of ram (sources vary on this value).

EPYC 8004 series

| Model | cores /threads |

base/boost frequency |

L3 cache Mbyte |

default power |

power range |

operating temp |

| 8534P | 64/128 | 2.3/3.1GHz | 128 | 200W | 155-225W | 0 to 75°C |

| 8534PN | 64/128 | 2.0/3.1 | 128 | 175 | – | -5 to 85 |

| 8434P | 48/96 | 2.5/3.1 | 128 | 200 | 155-225 | 0 to 75 |

| 8434PN | 48/96 | 2.0/3.0 | 128 | 155 | – | -5 to 85 |

| 8324P | 32/64 | 2.65/3.0 | 128 | 180 | 155-225 | 0 to 75 |

| 8324PN | 32/64 | 2.05/3.0 | 128 | 130 | – | -5 to 85 |

| 8224P | 24/48 | 2.55/3.0 | 64 | 160 | 155-225 | 0 to 75 |

| 8224PN | 24/48 | 2.0/3.0 | 64 | 120 | – | -5 to 85 |

| 8124P | 16/32 | 2.45/3.0 | 64 | 125 | 120-150 | 0 to 75 |

| 8124PN | 16/32 | 2.0/3.0 | 64 | 100 | – | -5 to 85 |

| 8024P | 8/16 | 2.4/3.0 | 32 | 90 | 70-100 | 0 to 75 |

| 8024PN | 8/16 | 2.05/3.0 | 32 | 80 | – | -5 to 85 |

Find an 8004 series architectural overview here